Forskrift

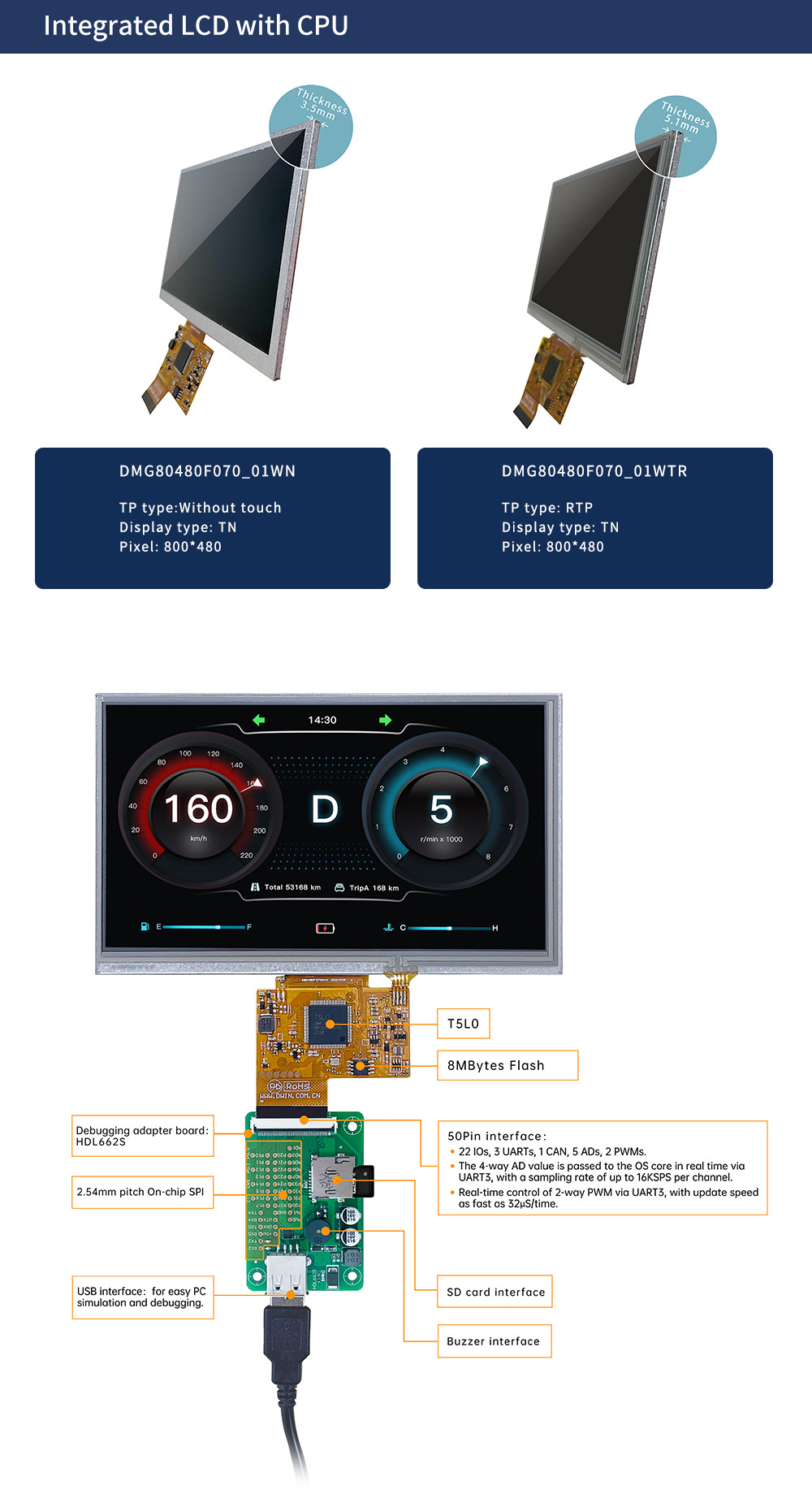

| T5L0 ASIC | Hannað af DWIN.Fjöldaframleiðsla árið 2020, 1MBytes Nor Flash á flísinni, 128Kbytes breytilegt geymslupláss til að skiptast á gögnum með OS CPU Core og minni.Endurskrifa hringrás: yfir 100.000 sinnum | ||

| Litur | 262K litir | ||

| LCD gerð | TN, TFT LCD | ||

| Skoðunarhorn | Venjulegt sjónarhorn, dæmigert gildi 70°/70°/30°/40°(L/R/U/D) | ||

| Sýningarsvæði(AA) | 154,08 mm (B)×85,92 mm (H) | ||

| Upplausn | 800×480 | ||

| Baklýsing | LED | ||

| Birtustig | DMG80480F070_01WN: 250nit | ||

| DMG80480F070_01WTR: 200nit | |||

| Gerð | RTP (resistive touch panel) | ||

| Uppbygging | ITO filma + ITO gler | ||

| Snertistilling | Stuðningspunktur snerta og draga | ||

| Yfirborðshörku | 3H | ||

| Ljóssending | Yfir 80% | ||

| Lífið | Punktur > 1.000.000 sinnum;Heilablóðfall > 100.000 sinnum;150g kraftur, bak og áfram talið tvisvar | ||

| Rafspenna | 3,6~5,5V | ||

| Aðgerð núverandi | VCC = +5V, Kveikt á baklýsingu, 410mA | ||

| VCC = +5V, Baklýsing slökkt, 115mA | |||

| Vinnuhitastig | -10 ℃ ~ 60 ℃ | ||

| Geymslu hiti | -20℃ ~ 70℃ | ||

| Vinnandi raki | 10% ~ 90% RH, dæmigerð gildi 60% RH | ||

| Baudrate | 3150~3225600 bps | ||

| Útgangsspenna | Output 1, Iout = 8mA;3,0~3,3V | ||

| Output 0, Iout =-8mA;0~0,3V | |||

| Inntaksspenna(RXD) | Inntak 1;3.3V | ||

| Inntak 0;0~0,5V | |||

| Viðmót | UART2: TTL; | ||

| UART4: TTL;(Aðeins fáanlegt eftir uppsetningu stýrikerfis) | |||

| UART5: TTL; (Aðeins í boði eftir uppsetningu stýrikerfis | |||

| Gagnasnið | UART2: N81; | ||

| UART4: N81/E81/O81/N82;4 stillingar (OS stillingar) | |||

| UART5: N81/E81/O81/N82;4 stillingar (OS stillingar) | |||

| Innstunga | 50Pin_0.5mm FPC | ||

| Flash | 8M bæti | ||

| PIN | Skilgreining | I/O | Virkni lýsing |

| 1 | +5V | I | Aflgjafi, DC3,6-5,5V |

| 2 | +5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 inntak ADC.12 bita upplausn ef um 3,3V aflgjafa er að ræða.0-3,3V inntak Spenna.Fyrir utan AD6 eru restin gögn send til OS kjarna í gegnum UART3 in rauntíma með 16KHz sýnatökutíðni.AD1 og AD5 er hægt að nota í samhliða, og AD3 og AD7 er hægt að nota samhliða, sem jafngildir tveimur 32KHz sýnatöku AD.AD1, AD3, AD5, AD7 er hægt að nota samhliða, sem jafngildir 64KHz sýnatöku AD;gögnin eru tekin saman 1024 sinnum og síðan deilt með 64 til að fá 64Hz 16bit AD gildi með ofsýni. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD1 | I | |

| 11 | +3.3 | O | 3,3V úttak, hámarksálag 150mA. |

| 12 | SPK | O | Ytri MOSFET til að keyra hljóðmerki eða hátalara.Ytri 10K viðnám ætti að draga niður til jarðar til að tryggja að kveikja sé á lágu stigi. |

| 13 | SD_CD | IO | SD/SDHC tengi, SD_CK tengir 22pF þétta við GND nálægt SD-kortsviðmótið. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | IO | |

| 16 | SD_D2 | IO | |

| 17 | SD_D1 | IO | |

| 18 | SD_D0 | IO | |

| 19 | PWM0 | O | 2 16 bita PWM úttak.Ytri 10K viðnám ætti að draga niður að jörðu til að tryggja að virkjun sé lágt.Hægt er að stjórna stýrikerfiskjarnanum í rauntíma í gegnum UART3 |

| 20 | PWM1 | O | |

| 21 | P3.3 | IO | Ef þú notar RX8130 eða SD2058 I2C RTC til að tengjast báðum IO, ætti SCL að vera tengdur við P3.2 og SDA tengdur við P3.3 samhliða með 10K resistor pull-up að 3,3V. |

| 22 | P3.2 | IO | |

| 23 | P3.1/EX1 | IO | Það er hægt að nota sem ytri truflun 1 inntak á sama tíma, og styður bæði lágspennustig eða truflunarstillingar á aftari brún. |

| 24 | P3.0/EX0 | IO | Það er hægt að nota sem ytri truflun 0 inntak á sama tíma, og styður bæði lágspennustig eða truflunarstillingar á aftari brún. |

| 25 | P2.7 | IO | IO tengi |

| 26 | P2.6 | IO | IO tengi |

| 27 | P2.5 | IO | IO tengi |

| 28 | P2.4 | IO | IO tengi |

| 29 | P2.3 | IO | IO tengi |

| 30 | P2.2 | IO | IO tengi |

| 31 | P2.1 | IO | IO tengi |

| 32 | P2.0 | IO | IO tengi |

| 33 | P1.7 | IO | IO tengi |

| 34 | P1.6 | IO | IO tengi |

| 35 | P1.5 | IO | IO tengi |

| 36 | P1.4 | IO | IO tengi |

| 37 | P1.3 | IO | IO tengi |

| 38 | P1.2 | IO | IO tengi |

| 39 | P1.1 | IO | IO tengi |

| 40 | P1.0 | IO | IO tengi |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | IO | IO tengi |

| 46 | P0.1 | IO | IO tengi |

| 47 | CAN_TX | O | CAN tengi |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (UART2 raðtengi OS kjarna) |

| 50 | UART2_RXD | I |