Forskrift

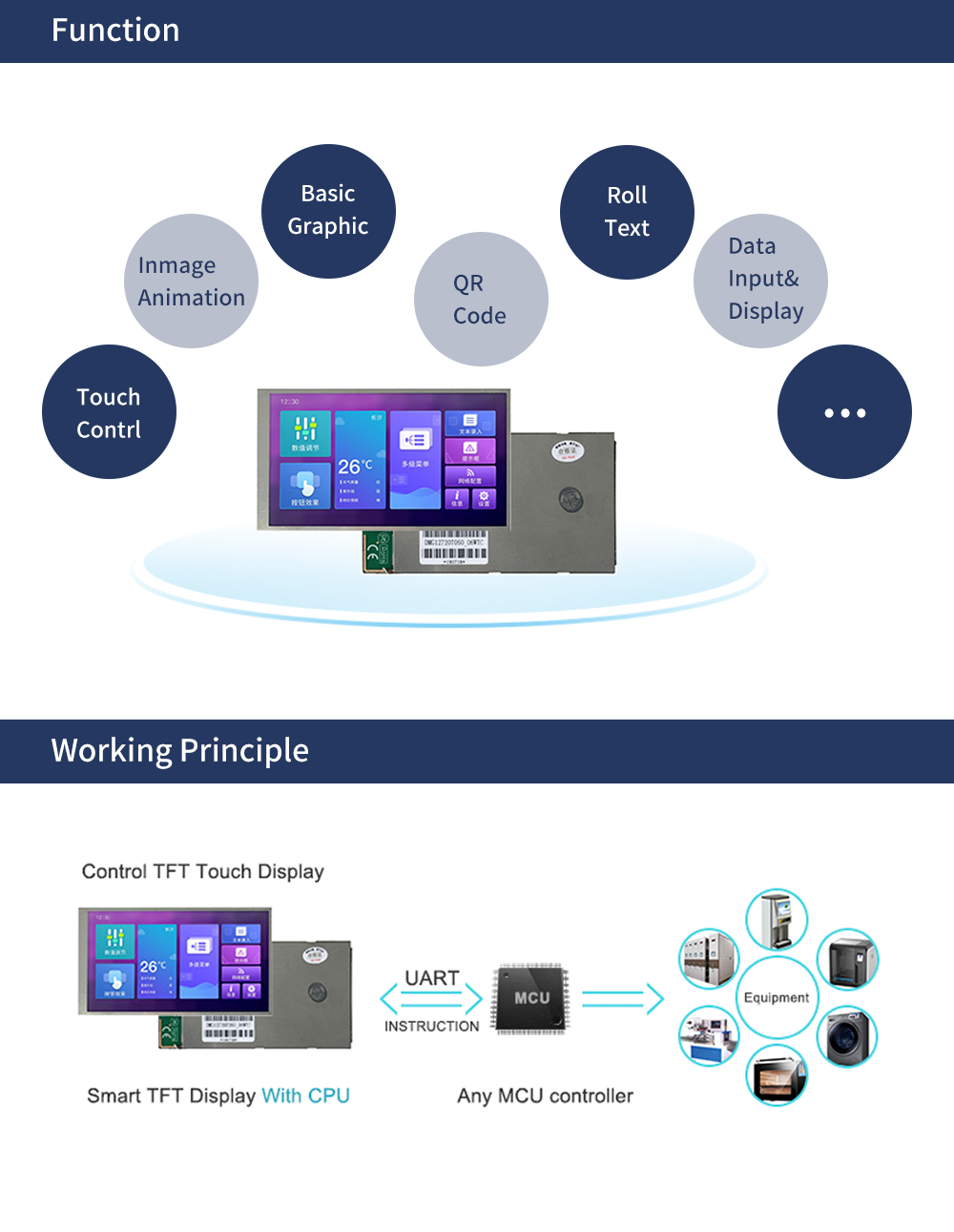

| T5L0 ASIC | T5L0 ASIC er afllítil, hagkvæmur, GUI og forrit mjög samþætt eins-flís tvíkjarna ASIC hannað af DWIN Technology fyrir lítinn stærð LCD og fjöldaframleitt árið 2020. | ||

| Litur | 262K litir | ||

| LCD gerð | IPS-TFT-LCD | ||

| Skoðunarhorn | Breiður skoðunarengill, dæmigerð gildi 85°/85°/85°/85°(L/R/U/D) | ||

| Sýningarsvæði(AA) | 71,86 mm (B)×70,18 mm (H) | ||

| Upplausn | 480*480 | ||

| Baklýsing | LED | ||

| Birtustig | DMG48480F040_01WTC:200nit DMG48480F040_01WTCZ01:200nit DMG48480F040_01WTCZ02:50nit DMG48480F040_01WN:250nit | ||

| Gerð | CTP (Kapacitive Touch Panel) | ||

| Uppbygging | G+G uppbygging | ||

| Snertistilling | Stuðningspunktur snerta og draga | ||

| Yfirborðshörku | 6H | ||

| Ljóssending | Yfir 90% | ||

| Lífið | Yfir 1.000.000 sinnum snerting | ||

| Rafspenna | 3,6 ~ 5,5V, dæmigert gildi 5V | ||

| Aðgerð núverandi | 245mA, VCC=5V, hámarks baklýsing | ||

| 75 mA, VCC=5V, baklýsing slökkt | |||

| Vinnuhitastig | -10 ~ 60 ℃ |

| Geymslu hiti | -20 ~ 70 ℃ |

| Vinnandi raki | 10%~90%RH |

| Notendaviðmót | 50Pin_0.5mm FPC | ||

| Baudrate | 3150~3225600 bps | ||

| Útgangsspenna | Úttak 1;3,0~3,3 V | ||

| Úttak 0;0~0,3 V | |||

| Inntaksspenna (RXD) | Inntak 1;3.3V | ||

| Inntak 0;0~0,5V | |||

| Viðmót | UART2: TTL; UART4: TTL;(Aðeins fáanlegt eftir uppsetningu stýrikerfis) UART5: TTL; (Aðeins í boði eftir uppsetningu stýrikerfis | ||

| Gagnasnið | UART2: N81; UART4: N81/E81/O81/N82;4 stillingar (OS stillingar) UART5: N81/E81/O81/N82;4 stillingar (OS stillingar) | ||

| Pinna | Skilgreining | I/O | Virkni lýsing |

| 1 | 5V | I | Aflgjafi, DC3,6-5,5V |

| 2 | 5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 inntak ADC.12 bita upplausn ef um 3,3V aflgjafa er að ræða.0-3,3V inntaksspenna.Fyrir utan AD6 eru restin gögn send til OS kjarna í gegnum UART3 í rauntíma með 16KHz sýnatökutíðni.AD1 og AD5 er hægt að nota samhliða og AD3 og AD7 er hægt að nota samhliða, sem jafngildir tveimur 32KHz sýnatöku AD.AD1, AD3, AD5, AD7 er hægt að nota samhliða, sem jafngildir 64KHz sýnatöku AD;gögnin eru lögð saman 1024 sinnum og síðan deilt með 64 til að fá 64Hz 16bit AD gildi með ofsýni. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD2 | I | |

| 11 | 3.3 | O | 3,3V úttak, hámarksálag 150mA. |

| 12 | SPK | O | Ytri MOSFET til að keyra hljóðmerki eða hátalara.Ytri 10K viðnám ætti að draga niður til jarðar til að tryggja að kveikja sé á lágu stigi. |

| 13 | SD_CD | I/O | SD/SDHC tengi, SD_CK tengir 22pF þétta við GND nálægt SD kortsviðmótinu. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | I/O | |

| 16 | SD_D2 | I/O | |

| 17 | SD_D1 | I/O | |

| 18 | SD_D0 | I/O | |

| 19 | PWM0 | O | 2 16 bita PWM úttak.Ytri 10K viðnám ætti að draga niður til jarðar til að tryggja að kveikja sé á lágu stigi. Hægt er að stjórna stýrikerfiskjarnanum í rauntíma í gegnum UART3 |

| 20 | PWM1 | O | |

| 21 | P3.3 | I/O | Ef þú notar RX8130 eða SD2058 I2C RTC til að tengjast báðum IO, ætti SCL að vera tengdur við P3.2 og SDA tengdur við P3.3 samhliða 10K viðnámsuppdrætti að 3.3V. |

| 22 | P3.2 | I/O | |

| 23 | P3.1/EX1 | I/O | Það er hægt að nota sem utanaðkomandi truflun 1 inntak á sama tíma og styður bæði lágspennustig eða truflunarstillingar á aftari brún. |

| 24 | P3.0/EX0 | I/O | Það er hægt að nota sem utanaðkomandi truflun 0 inntak á sama tíma og styður bæði lágspennustig eða truflunarstillingar á aftari brún |

| 25 | P2.7 | I/O | IO tengi |

| 26 | P2.6 | I/O | IO tengi |

| 27 | P2.5 | I/O | IO tengi |

| 28 | P2.4 | I/O | IO tengi |

| 29 | P2.3 | I/O | IO tengi |

| 30 | P2.2 | I/O | IO tengi |

| 31 | P2.1 | I/O | IO tengi |

| 32 | P2.0 | I/O | IO tengi |

| 33 | P1.7 | I/O | IO tengi |

| 34 | P1.6 | I/O | IO tengi |

| 35 | P1.5 | I/O | IO tengi |

| 36 | P1.4 | I/O | IO tengi |

| 37 | P1.3 | I/O | IO tengi |

| 38 | P1.2 | I/O | IO tengi |

| 39 | P1.1 | I/O | IO tengi |

| 40 | P1.0 | I/O | IO tengi |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | I/O | IO tengi |

| 46 | P0.1 | I/O | IO tengi |

| 47 | CAN_TX | O | CAN tengi |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (UART0 raðtengi OS kjarna) |

| 50 | UART2_RXD | I |